Sometimes Hoodoo Rituals Are Needed to Implement New Technology Features in OpenVPX Chassis

David Hinkle January 24, 2017

- Rapidly changing technologies have increased the system design challenge

- VICTORY: Vehicle Data Bus; MORA: Modular Open Radio Architecture

- SWaPc is a Systems Concept not just an Acronym

- Size, Weight, Power and Cost

- Packaging Expertise has evolved to require System Expertise

- Solutions require the integration of payload boards from the Customer and Elma partners, mated with the system chassis, custom backplane and cable set using mixed I/O.

- Design trades offs occur at several levels, and become a Set of considerations. Commercial boards can be unknown(in design)

- Transfer rates over the distances are new to the design

## What Gate's System Designs

- System Design Starts with a Physical Concept Drawing

- Backplane transmission rate: modeling and simulation

- End-to-end use case from: board to backplane to board

- Materials, design techniques, fabrication method, connectors

- Model and simulate to review performance against targets

- Thermal simulation and modeling

- Power In

Power Out

- Removing heat and cooling scheme

- I/O Design and Method

- Connector choice to match signal speed

- Finding the connectors, and promote sources

- Copper vs Fiber; Digital vs Analog

- Compatible cable solutions and contacts that are new

# Apply New I/O Connectors

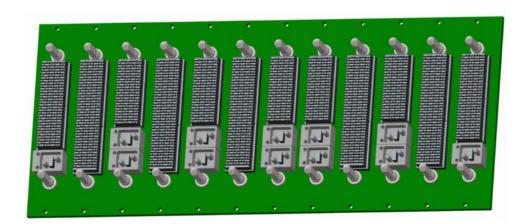

# VITA 67.1 and 67.2 Module Connectors can mate with VITA 67.3 Backplane Connectors

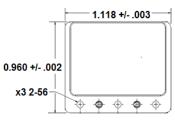

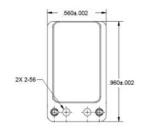

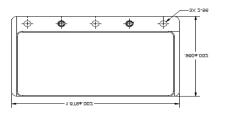

VITA 67.1

VITA 67.2

VITA 67.3C

#### Module 67.3d

Module 67.3e

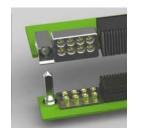

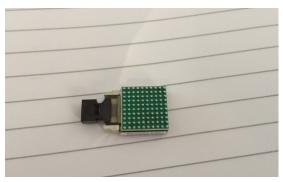

- Reflex Photonics Transceiver with MT Ferrule

- Multiple Fibers per Ferrule

- 12 to 64 per Ferrule

- MT to Circular allows termination to the bulkhead

- VITA 66.4 and VITA 67.3 define Connectors

- Surface Mount BGA Package

- 40C to +85C

- Allows Fiber I/O from VPX board to bulkhead or Board to Board

- Applicable for 10Gb, 40Gb, Required for 100Gb Ethernet

- Mitigate development risk

- Find a set of resources to build a team

- Meet objective and threshold goals of the system design

- Build a supply team to vet ideas, and vet the requirements against possible solutions

- Progressively reduce risk thru the design effort

- New technology required

- Need to innovate

- Applying new standards for the first time

- Standards don't exist yet (not ratified)

- Ecosystem has not solved the application problem yet

- Needs components that are next generation

- End-to-End Solution is required Board to Backplane to Board

## **Overview - Complex Systems: H/W Convergence**

#### • Technology Drivers

- Establish the Setting and the Frame the need

### • Gating Factors and Tools

- Speed, Size, and Power, Performance

- Modeling and Simulation Tools Needed

- Dialing in the Specifications and Design

### • Component Supplier vs. Partner

- Finding a suitable set of partners for App

### Integration Needs

- New Technology and Increased performance drives Higher Cooperation and Interchange between supply team members

- Agile Design and Scrum techniques are necessary internally and externally

Expertise in VPX Change Agent for Specification Ability to Model and Simulate Identifying Partners Build House

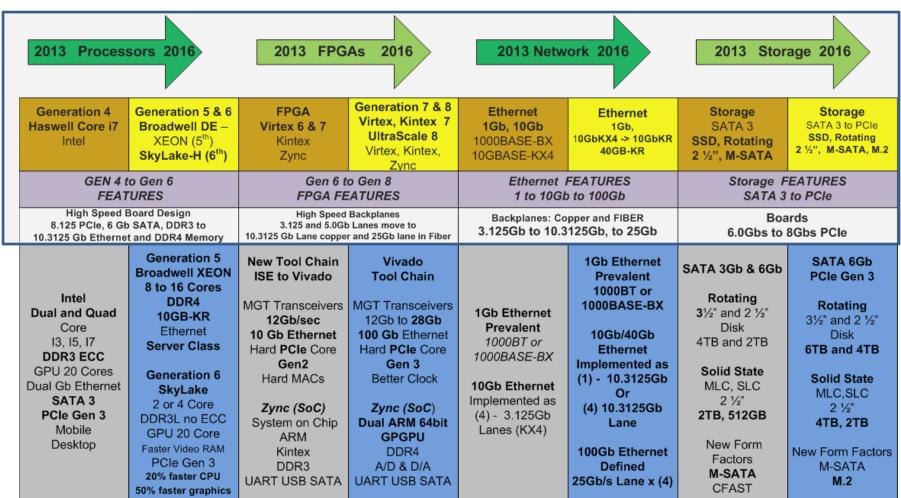

## **Technology Trends – Where are You?**

Core Technology Transition by Category

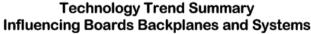

#### **Networking Trends** 10Gb to 100Gb Ethernet : Current is 1/10/40Gb

#### • New SBC and Switch Chip Devices ----

- Allow new designs with more function

- Examples Include:

- Servers on a Chip: Xeon D multi-core processor

- High speed Ethernet switches now available in 3U VPX provide necessary connectivity

- FPGA System on Chip solution allow entire sub-systems to be placed on a 3U card

### **Complex Solution Summary**

- VPX is evolving to support new architectures

- New I/O types are being supported in VPX allowing high density fiber to be used

- **RF I/O is supported for Mezzanines with VITA 67.3**

- New VPX connectors will provide a path to support PCIe Gen 4

- High Speed backplanes can be built to support the bandwidth, and I/O connectors required by new architectures

- VPX systems will provide the feature set to be the platform for long life cycle systems

- Greater Use of Fiber Optic I/O Going Forward

- 100Gb Ethernet requires 25Gb per lane requiring fiber optic I/O to implement off board connections

- Next Generation Multi-Gig connector will not support this rate

- PCIe Gen 4

- Doubles bandwidth from 8 GT/s per lane to 16 GT/sec per lane □ BW per lane 2GB/s

- New Multi-Gig Connector required for next generation protocols

- T/E connectivity indicates the design is being worked

# Thank you for your time!

14 www.elma.com